|

1) Logique des entrées - sorties du microcontrôleur

68HC11F1 programmé :

CLIQUEZ SUR L'IMAGE CI-DESSUS

POUR L'AGRANDIR

CLIQUEZ SUR L'IMAGE CI-DESSUS

POUR L'AGRANDIR

Téléchargement

du soft destiné au microcontrôleur

68HC11F1 :

Téléchargement du programme MM10.S19

du 68HC11F1 :  MM10.ZIP 490 octets

MM10.ZIP 490 octets

AVIS

: Le programme source (code

assembleur) ne sera pas diffusé.

2) Données parallèles décodées en sortie :

Les deux ports B et F

permettent de récupérer la trame décodée sous forme parallèle avec le LSB = B0 et le

MSB = F3. La correspondance des bits de l'encodeur MM53200 ou UM3750A avec les deux ports

du décodeur 68HC11F1 est la suivante : Les deux ports B et F

permettent de récupérer la trame décodée sous forme parallèle avec le LSB = B0 et le

MSB = F3. La correspondance des bits de l'encodeur MM53200 ou UM3750A avec les deux ports

du décodeur 68HC11F1 est la suivante :

|

Broches du

circuit encodeur MM53200 / UM3750A

|

1

|

2

|

3

|

4

|

5

|

6

|

7

|

8

|

9

|

10

|

11

|

12

|

|

Correspondance

des bits en sortie du décodeur 68HC11F1

|

B0

|

B1

|

B2

|

B3

|

B4

|

B5

|

B6

|

B7

|

F0

|

F1

|

F2

|

F3

|

Pour la fiabilité du système, l'état des 12

sorties parallèles (PORTB et F) se modifie qu'après la réception consécutive de 3 trames identiques.

Pour la fiabilité du système, l'état des 12

sorties parallèles (PORTB et F) se modifie qu'après la réception consécutive de 3 trames identiques.

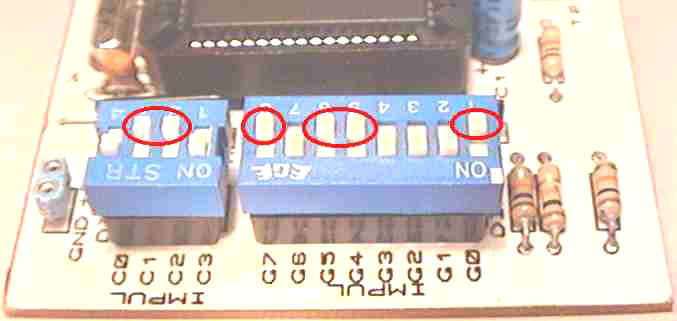

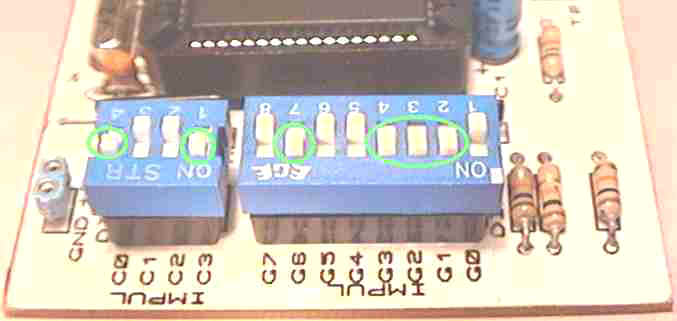

3) Mode STABLE et IMPULSIONNEL :

Mode

STABLE = 1 (PORTG0 à PORTG7 = 1 et PORTC0 à PORTC3 = 1). Niveau logique des sorties //

(PORTB et F) en mode STABLE : Mode

STABLE = 1 (PORTG0 à PORTG7 = 1 et PORTC0 à PORTC3 = 1). Niveau logique des sorties //

(PORTB et F) en mode STABLE :

Recopie fidèle des bits de

codage pendant la réception des trames séries.

Maintien des derniers états logiques des bits en cas

d'arrêt volontaire ou involontaire des trames séries.

Exemple : Les bits C1,

C2, G7, G3, G2, G0 sont positionnés en mode STABLE (les

inters de programmation concernés sont ouverts). Ainsi les sorties F1, F2,

B7, B3, B2, B0 maintiennent leurs états logiques en l'absence des données

séries.

Mode IMPULSIONNEL

= 0 (PORTG0 à PORTG7 = 0 et PORTC0 à PORTC3 = 0). Etat logique des sorties // (PORTB et

F) en mode IMPULSIONNEL : Mode IMPULSIONNEL

= 0 (PORTG0 à PORTG7 = 0 et PORTC0 à PORTC3 = 0). Etat logique des sorties // (PORTB et

F) en mode IMPULSIONNEL :

Recopie fidèle des bits de codage pendant la réception

des trames séries.

Recopie fidèle des bits de codage pendant la réception

des trames séries.

Remise à zéro des bits en cas d'arrêt volontaire ou

involontaire des trames séries.

Remise à zéro des bits en cas d'arrêt volontaire ou

involontaire des trames séries.

Exemple : En reprenant

l'exemple précédent, les bits C0, C3, G6, G5, G4, G1 sont positionnés

en mode IMPULSIONNEL (les inters de programmation

concernés sont fermés).

Ainsi les sorties F0, F3, B6, B5, B4, B1 sont remises à l'état bas en

l'absence des données séries.

4) Validation des données séries reçues en entrée

A0 :

On reçoit des trames séries conformes : les sorties PD2

= 1 et PD3 = 0 du PORTD.

On reçoit des trames séries conformes : les sorties PD2

= 1 et PD3 = 0 du PORTD.

On ne reçoit pas de trames conformes ou rien : les sorties PD2

= 0 et PD3 = 1 du PORTD.

On ne reçoit pas de trames conformes ou rien : les sorties PD2

= 0 et PD3 = 1 du PORTD.

Vous pouvez utiliser l'un de ces

signaux pour visualiser la bonne réception des trames séries. Cependant, une interface à base de transistors est insérée entre PD2

et la sortie D2 puis entre PD3 et la sortie D3 du circuit imprimé. Voir [

Application

]

pour un exemple

de câblage élémentaire des sorties D2 et D3.

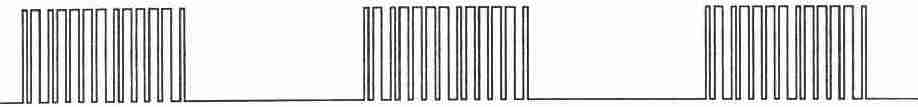

L'entrée A0 reçoit

la trame série. La "polarité" de cette trame générée par un encodeur

MM53200 ou UM3750A respecte :

- des pauses de silence à l'état bas de 11,52 ms ,

- des salves de 11,52 ms (12 bits + 1 bit

d'initialisation) intercalées entre chaque pauses.

5) Reset et alimentation de la carte :

Une réinitialisation du microcontrôleur s'effectue en

court-circulant les deux picots RST. En fonctionnement normal, les deux picots doivent

rester ouvert.

Une réinitialisation du microcontrôleur s'effectue en

court-circulant les deux picots RST. En fonctionnement normal, les deux picots doivent

rester ouvert.

L'alimentation de la carte doit se faire

sous +5V filtré et régulé. Le courant absorbé est de l'ordre de 15 mA.

L'alimentation de la carte doit se faire

sous +5V filtré et régulé. Le courant absorbé est de l'ordre de 15 mA.

6) Oscillateur de l'encodeur MM53200 ou

UM3750A :

Le montage chargé d'émettre la trame

série est composé d'un MM53200 ou UM3750A. La transmission de cette trame peut se faire

par liaisons filaires, HF, infra-rouge, ultra-sonore, etc...

En patte n°13 de

l'encodeur placez une résistance de 100 kohms reliée à l'alimentation

et une capacité céramique de 180 pF reliée à la masse. Leurs

tolérances ne doivent pas excéder les 5%. Pensez y, c'est souvent la source d'une panne ou d'un

fonctionnement erratique du décodeur !!!

|