|

Présentation

succincte du circuit logique programmable

CPLD - ispLSI1024-80LJ : Présentation

succincte du circuit logique programmable

CPLD - ispLSI1024-80LJ :

La

famille des composants ispLSI

conçue par la firme Lattice

existe depuis plus d'une bonne vingtaine

d'année. L'abréviation

ispLSI

signifie In

System

Programmable

LSI.

En effet, il est possible de procéder

à la programmation

du dit composant alors qu'il

est déjà implanté

dans le montage dont il constitue

l'intelligence en quelque sorte !

La seconde partie

de la dénomination LSI,

signifie Large

Scale

Integration,

c'est à dire intégration

à grande échelle, ce qui

met l'accent sur la densité importante

de l'intégration des dits composants.

La

famille de composants ispLSI

se différencie au niveau des GLB

Generic

Logic

Blocs

pour blocs de logique générique.

Pour le ispLSI

1024

retenu dans ce projet, il dispose de 24

GLB,

de 48

entrées / sorties et

de 6 entrées d'horloge.

Synoptique

fonctionnel du ispLSI

1024

comportant

grand nombres de fonctions logiques

intégrée.

Le

composant comporte

plusieurs connexions d'entrées

/ sorties

à la fonctionnalité universelle.

Ces connexions sont reliées aux

cellules d'entrées / sorties

configurables à volonté

en bascule

bistable

(flip-flop) ou en verrou

par exemple. En cas d'inutilisation

d'une entrées / sorties il y

a

activation automatique d'une

résistance de rappel au

niveau logique haut permettant ainsi

de limiter le bruit dans le circuit.

Brochage

du ispLSI

1024 - 80 LJ

Sa

fréquence

de fonctionnement peut

monter jusqu'à

80MHz

pour un

temps de propagation

moyen dans le circuit de 12ns.

Néanmoins ce temps de propagation

peut être réduit

à quelques nanosecondes

en choisissant judicieusement

les fonctions logiques

que l'on souhaite implanter en interne

par programmation. Comme nous l'avons

déjà abordé à

la page

[

La

théorie du générateur

] la

synthèse

numérique directe

(ou DDS) nécessite une

circuiterie logique

possédant un temps

de propagation extrêmement court.

Nous

avons estimé que ce

CPLD avait remplacé avantageusement

une douzaine

de

circuits logiques dont la plupart en

technologie Fast-TTL.

De la sorte, nous avons réduit

la taille du circuit imprimé

et la consommation globale du montage

pour un coût final moindre.

Bref, ce circuit présente un certain

nombre d'avantages, surtout lorsque

cette faculté n'implique pas

de gros investissements.

Programmation

du ispLSI 1024 - 80 LJ : Programmation

du ispLSI 1024 - 80 LJ :

La

programmation du circuit Lattice ne

nécessite pas non plus d'investissements

monstrueux et mieux encore, la

totalité de l'électronique

de programmation

nécessaire se résume à

un unique

tampon TTL

entouré de quelques

composants passifs.

Cette interface porte le nom d'interface

JTAG

pour Joint

Test

Action

Group.

Interface

JTAG : Interface

JTAG :

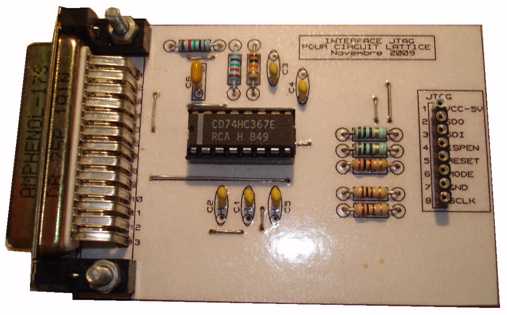

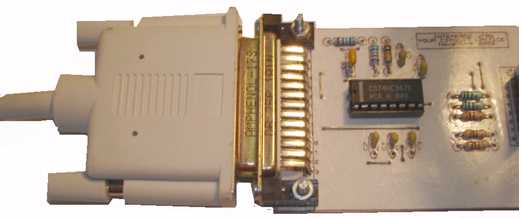

Voici

la totalité du schéma

de l'interface nécessaire au

circuit logique ispLsi

1024.

Nous retrouvons à gauche l'embase DB25

mâle,

au centre le tampon composé d'un 74HC367

et quelques résistances

et condensateurs.

Cliquez sur l'image

ci-dessus pour ouvrir le fichier PDF

du schéma

Cette

interface JTAG

vient se connecter sur le port Centronics

(parallèle)

de votre ordinateur. Si vous n'avez

plus de port Centronics sur votre PC,

vous ne pourrez pas utiliser de convertisseur

USB / Centronics car cela ne fonctionne

pas avec le logiciel de Lattice. Ainsi, si vous

ne pouvez pas programmer votre ispLsi

1024,

vous pouvez à défaut nous

faire parvenir votre ispLsi

1024 pour une programmation gracieuse

en suivant la procédure

décrite à la page

[

Logiciels

].

Nomenclature

de l'interface JTAG :

Nomenclature

de l'interface JTAG :

Résistances 1/4W - 5%

:

100

: R4, R5, R6, R7, R8

10k

: R1, R2, R3

Condensateurs plastiques

LCC :

100nF : C6

Condensateurs

céramiques :

560pF

: C1, C2, C3, C4, C5

Circuit intégré

:

74HC367

: U1 + support lyre 16 broches.

Divers

:

J1

: connecteurs sub-D mâles coudé

JTAG

: barrette de 8 picots tulipes

Une

nappe souple composée de 8 brins

Circuit imprimé simple face : 78 x 54

Aspect

de l'implantation et du typon de l'interface

JTAG :

Aspect

de l'implantation et du typon de l'interface

JTAG :

Téléchargement

du schéma, implantation et typon

au format PDF :

Téléchargement

du schéma, implantation et typon

au format PDF :

Schéma de principe de l'interface

JTAG :

Schéma de principe de l'interface

JTAG :  75

ko 75

ko

Implantation de l'interface JTAG

: Implantation de l'interface JTAG

:  12

ko 12

ko

Cuivre de l'interface JTAG :

Cuivre de l'interface JTAG :  40

ko 40

ko

[ COMMANDER LE CIRCUIT IMPRIME

]

Téléchargement

du logiciel ispLever Classic depuis

le

site de Lattice : Téléchargement

du logiciel ispLever Classic depuis

le

site de Lattice :

L'ensemble

des outils logiciels

nécessaires au développement

et à la programmation de l'ispLSI

1024 sont disponibles en

libre téléchargement sur

le site de [

Lattice

].

La partie logicielle permettant de programmer

le IspLSI ne nécessite pas de

disposer d'une licence.

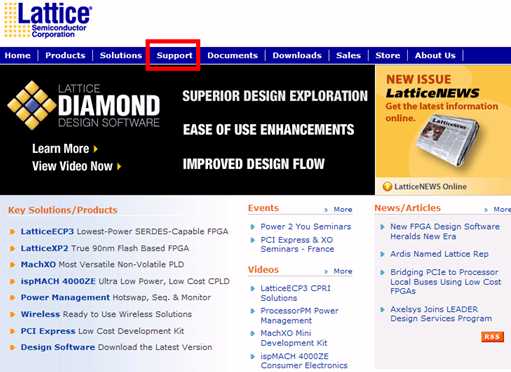

A

partir de la page web du site internet

de Lattice, cliquez sur Support

comme encadré ci-dessous :

A

partir de la page web du site internet

de Lattice, cliquez sur Support

comme encadré ci-dessous :

Cliquez sur l'image

ci-dessus pour l'agrandir

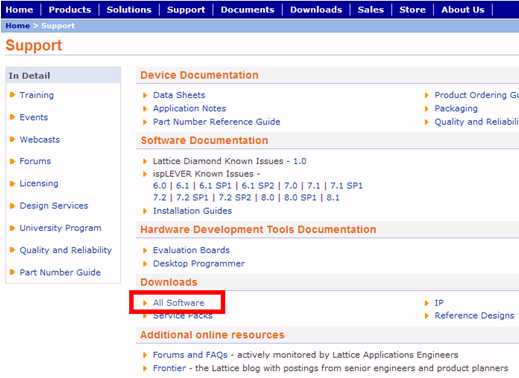

Cliquez

sur All

Software

comme encadré ci-dessous :

Cliquez

sur All

Software

comme encadré ci-dessous :

Cliquez sur l'image

ci-dessus pour l'agrandir

Cliquez

sur

ispLever-Classic

comme encadré ci-dessous :

Cliquez

sur

ispLever-Classic

comme encadré ci-dessous :

Cliquez sur l'image

ci-dessus pour l'agrandir

Cliquez

enfin sur ispLEVER

Classic Base Module

comme encadré ci-dessous :

Cliquez

enfin sur ispLEVER

Classic Base Module

comme encadré ci-dessous :

Cliquez sur l'image

ci-dessus pour l'agrandir

Lorsque

le téléchargement de ispLEVER

Classic Base Module est

terminé, il ne vous reste plus

qu'à installer le logiciel sur

votre PC. L'installation est longue,

soyez patient...

Une

fois installé, vous obtenez différentes

applications dans

la liste des programmes de votre PC

comme ci-dessous :

Cliquez sur l'image

ci-dessus pour l'agrandir

Connexion

de l'interface JTAG au générateur

de fonctions : Connexion

de l'interface JTAG au générateur

de fonctions :

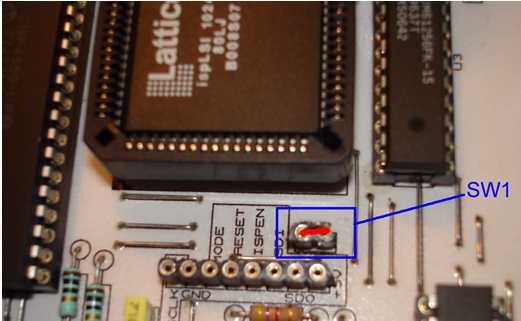

Hors

tension, court-circuitez

les picots

tulipes de SW1

de votre générateur de

fonctions comme ci-dessous

: Hors

tension, court-circuitez

les picots

tulipes de SW1

de votre générateur de

fonctions comme ci-dessous

:

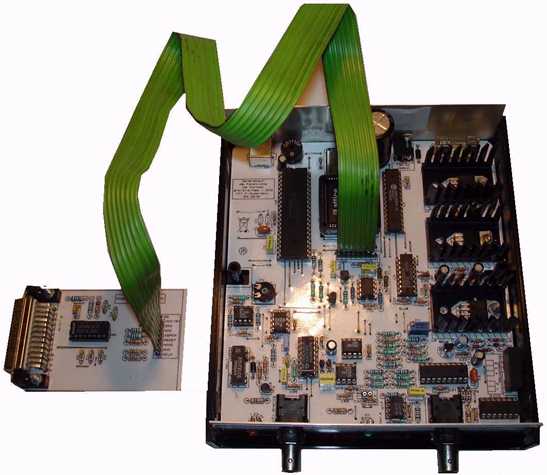

Au

moyen d'une

nappe souple composée de 8 brins,

reliez le connecteur

de

l'interface JTAG au connecteur référencé

K4

du générateur de fonction

comme ci-dessous : Au

moyen d'une

nappe souple composée de 8 brins,

reliez le connecteur

de

l'interface JTAG au connecteur référencé

K4

du générateur de fonction

comme ci-dessous :

Cliquez sur l'image

ci-dessus pour l'agrandir

Prenez garde de connecter les

deux extrémités de la

nappe dans le bon sens.

Le croquis ci-dessous illustre

les connexions à réaliser

entre l'interface JTAG à gauche

et le connecteur K4 du générateur

de fonctions à droite.

Prenez garde de connecter les

deux extrémités de la

nappe dans le bon sens.

Le croquis ci-dessous illustre

les connexions à réaliser

entre l'interface JTAG à gauche

et le connecteur K4 du générateur

de fonctions à droite.

Cliquez sur l'image

ci-dessus pour l'agrandir

Mettez

votre

ordinateur hors tension

et connectez un câble DB25

entre

votre PC et l'interface JTAG comme ci-dessous

: Mettez

votre

ordinateur hors tension

et connectez un câble DB25

entre

votre PC et l'interface JTAG comme ci-dessous

:

Remettez

votre

PC sous

tension

et attendez la fin du chargement de

Windows.... Mettez le générateur

de fonctions sous

tension. Remettez

votre

PC sous

tension

et attendez la fin du chargement de

Windows.... Mettez le générateur

de fonctions sous

tension.

Cela signifie que vous avez

auparavant dument

testé votre générateur

: absence de court-circuit sur le circuit

imprimé, soudures irréprochables,

tensions sur l'ensemble des circuits

correctes, etc...

Cela signifie que vous avez

auparavant dument

testé votre générateur

: absence de court-circuit sur le circuit

imprimé, soudures irréprochables,

tensions sur l'ensemble des circuits

correctes, etc...

Utilisation

du logiciel ispVM System permettant

de programmer le ispLSI 1024 : Utilisation

du logiciel ispVM System permettant

de programmer le ispLSI 1024 :

Lancez

le logiciel de Lattice intitulé

ispVM

System

comme encadré ci-dessous :

Lancez

le logiciel de Lattice intitulé

ispVM

System

comme encadré ci-dessous :

Quelques

instants après, vous devez obtenir

:

Quelques

instants après, vous devez obtenir

:

Cliquez sur l'image

ci-dessus pour l'agrandir

Cliquez

sur le bouton

Add Device (Ins)

comme encadré ci-dessous :

Cliquez

sur le bouton

Add Device (Ins)

comme encadré ci-dessous :

Cliquez

sur le bouton

Select...

puis choisissez la bonne référence

du circuit ispLSI

1024

en version PLCC

68

broches comme

ci-dessous :

Cliquez

sur le bouton

Select...

puis choisissez la bonne référence

du circuit ispLSI

1024

en version PLCC

68

broches comme

ci-dessous :

Cliquez

sur le bouton Browse

et sélectionnez le fichier Jedec

(GBF.JED) à programmer au sein

du circuit. Vous trouverez ce fichier

en libre téléchargement

à la page [

Logiciels

].

Cliquez

sur le bouton Browse

et sélectionnez le fichier Jedec

(GBF.JED) à programmer au sein

du circuit. Vous trouverez ce fichier

en libre téléchargement

à la page [

Logiciels

].

Cliquez

enfin sur le bouton Ok

afin de valider vos sélections.

Cliquez

enfin sur le bouton Ok

afin de valider vos sélections.

Effectuez

un

test de communication

avec l'interface JTAG. Pour ce faire,

cliquez dans le menu sur ispTools

puis sélectionnez

Board Diagnotics... comme

ci-dessous :

Effectuez

un

test de communication

avec l'interface JTAG. Pour ce faire,

cliquez dans le menu sur ispTools

puis sélectionnez

Board Diagnotics... comme

ci-dessous :

Si

le

test est concluant,

vous devez obtenir la recopie d'écran

suivante avec des cases

vides

dans la partie

encadrée en rouge

ci-dessous.

Si

le

test est concluant,

vous devez obtenir la recopie d'écran

suivante avec des cases

vides

dans la partie

encadrée en rouge

ci-dessous.

En

revanche, si vous obtenez des coches

dans ces cases, cela implique que vous

avez un disfonctionnement de la communication

sur la ligne concernée de l'interface

JTAG.

Si

le test précédent est

concluant, alors vous pouvez

lancer la programmation du

circuit suivie automatiquement par sa

vérification.

Pour ce faire, cliquez sur le bouton

GO,

comme encadré ci-dessous :

Si

le test précédent est

concluant, alors vous pouvez

lancer la programmation du

circuit suivie automatiquement par sa

vérification.

Pour ce faire, cliquez sur le bouton

GO,

comme encadré ci-dessous :

Durant

la phase de programmation, un

compteur s'incrémente

attestant de la bonne marche du processus.

Patientez jusqu'à la fin de la

programmation suivie de la vérification...

Durant

la phase de programmation, un

compteur s'incrémente

attestant de la bonne marche du processus.

Patientez jusqu'à la fin de la

programmation suivie de la vérification...

Hors

tension

(PC et générateur de fonctions),

retirez

la

nappe souple

et ôtez le

court-circuit que

vous avez placé précédemment

sur les picots tulipes de SW1

comme ci-dessous :

Hors

tension

(PC et générateur de fonctions),

retirez

la

nappe souple

et ôtez le

court-circuit que

vous avez placé précédemment

sur les picots tulipes de SW1

comme ci-dessous :

Désormais

le

ispLSI 1024

est programmé et

opérationnel.

Le

générateur de fonction

est prêt à fonctionner

à condition d'avoir également

programmé les deux

microcontrôleurs

U2

et U18.

Désormais

le

ispLSI 1024

est programmé et

opérationnel.

Le

générateur de fonction

est prêt à fonctionner

à condition d'avoir également

programmé les deux

microcontrôleurs

U2

et U18.

Consultez

la page [ Utilisation

]

pour

en savoir plus sur l'utilisation du

générateur de fonctions

arbitraires...

|